# Godson 3B1500 Processor User Manual

# Volume II

GS464 processor core V1.3

2016 Nian 4 Yue

Godson Technology Co., Ltd.

Copyright Notice

The copyright of this document belongs to Beijing Godson Technology Co., Ltd. and all rights are reserved. Without written permission, any company

No company or individual may make any part of this document public, reprint, or otherwise distribute to third parties. Otherwise, it will

Investigate its legal responsibility

#### Disclaimer

This document only provides periodic information, and the contents can be updated at any time according to the actual situation of the product without notice. Such as

The company does not assume any responsibility for direct or indirect losses caused by improper use of documents.

#### Godson Technology Co., Ltd.

Loongson Technology Corporation Limited

Address: Building 2 of Longxin Industrial Park, Zhongguancun Environmental Protection Technology Demonstration Park, Haidian District, Beijing

Building No.2, Loongson Industrial Park,

Zhongguancun Environmental Protection Park, Haidian District, Beijing

Phone (Tel): 010-62546668

Fax: 010-62600826

Page 3

Godson 3B1500 Processor User Manual • Volume 2

### Read the guide

"Longxin 3B1500 Processor User Manual" is divided into the first volume, the second volume, and software programming guide.

Godson 3B1500 Processor User Manual Booklet introduces Godson 3B1500 multi-core processor architecture, mainly including multi-core

Processor architecture and register description;

"Godson 3B1500 Processor User Manual" Book II, a detailed introduction from the perspective of system software developers

GS464 high-performance processor core used;

"Godson 3B1500 Processor User Manual" software programming guide introduces common issues in BIOS and operating system development

problem.

### Page 4

Godson 3B1500 Processor User Manual • Volume 2

### revise history

Godson 3B1500 processor user hands

Document update records Document name: bool

--Volume II

version number V1.3

founder: Chip R & D

Creation date: 2016-04-01

### Update history

| Serial numberpdated |                   | updater            | update content update content                                                      |

|---------------------|-------------------|--------------------|------------------------------------------------------------------------------------|

| 1                   | 2011-06-17        | R & D Center V1.0  | preliminary draft completed                                                        |

| 2                   | 2012-05-02        | R & D Center V1.1  | Fixed bugs related to 48-bit address space in Chapter 5, "Memory Management" error |

| 3                   | 2015-10-09 Chip l | R & D Department V | 1.2 Revised the description of instructions in Chapter 2 and Chapter 7             |

4 2016-04-01 The chip research and development department V1.3 adjusts some instructions according to LS3B1500G

Manual feedback: service@loongson.cn

### Page 5

#### Godson 3B1500 Processor User Manual • Volume 2

### table of Contents

| 1.        | <u>S</u>                                                                                                     | Structu                                 | re Overview 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |            |

|-----------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|

| <u>2.</u> | <u>C</u>                                                                                                     | <u>Overvi</u>                           | ew of Godson GS464 processor core instruction set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |            |

|           | <u>2.1.</u>                                                                                                  |                                         | <u>List of MIPS64 compatible instructions</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <u>5</u>    |            |

|           | 2                                                                                                            | 2.1.1.                                  | Fetch instruction5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |            |

|           | 2                                                                                                            | 2.1.2.                                  | Operation Instructions6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |            |

|           | 2                                                                                                            | 2.1.3.                                  | Branch and branch instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <u>9</u>    |            |

|           | 2                                                                                                            | 2.1.4.                                  | Coprocessor instructions11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |            |

|           | 2                                                                                                            | 2.1.5.                                  | Other instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |            |

|           | <u>2.2.</u>                                                                                                  |                                         | $\underline{MIPS64\ Compatible\ Instructions\ Implementation\ Instructions\}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13          |            |

|           | 2                                                                                                            | 2.2.1.                                  | There are instructions to implement the differences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 13        |            |

|           | 2                                                                                                            | 2.2.2.                                  | Disabled instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |            |

|           | <u>2.3.</u>                                                                                                  |                                         | <u>Custom extension instructions</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <u>. 16</u> |            |

|           | 2                                                                                                            | 2.3.1.                                  | Custom extended fetch instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <u>16</u>   |            |

|           | 2                                                                                                            | 2.3.2.                                  | Custom extended operation instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <u> 17</u>  |            |

|           | 2                                                                                                            | 2.3.3.                                  | Custom extended X86 binary translation acceleration instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |            |

|           | 2                                                                                                            | 2.3.4.                                  | Custom extended miscellaneous instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             | twenty one |

|           |                                                                                                              |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |            |

|           | 2                                                                                                            | 2.3.5.                                  | Custom extended 64-bit multimedia acceleration instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | twenty one  |            |

| <u>3.</u> | _                                                                                                            |                                         | ontrol register 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | twenty one  |            |

| <u>3.</u> | _                                                                                                            |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | twenty one  |            |

| <u>3.</u> | (                                                                                                            |                                         | ontrol register 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | twenty one  |            |

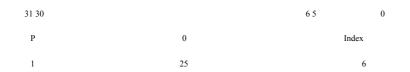

| <u>3.</u> | 3.1.                                                                                                         |                                         | <u>Index register (0, 0)</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | twenty one  |            |

| <u>3.</u> | 3.1.<br>3.2.                                                                                                 |                                         | Index register (0,0)       26         Random register (1,0)       27         EntryLo0 (2,0) and EntryLo1 (3,0) registers       28         Context (4,0)       29                                                                                                                                                                                                                                                                                                                                                                                      | twenty one  |            |

| <u>3.</u> | 3.1.<br>3.2.<br>3.3.                                                                                         |                                         | Index register (0, 0)       26         Random register (1, 0)       27         EntryLo0 (2,0) and EntryLo1 (3,0) registers       28         Context (4,0)       29         PageMask Register (5, 0)       29                                                                                                                                                                                                                                                                                                                                          | twenty one  |            |

| <u>3.</u> | 3.1.<br>3.2.<br>3.3.<br>3.4.                                                                                 |                                         | Index register (0,0)       26         Random register (1,0)       27         EntryLo0 (2,0) and EntryLo1 (3,0) registers       28         Context (4,0)       29                                                                                                                                                                                                                                                                                                                                                                                      | twenty one  |            |

| 3.        | 3.1.<br>3.2.<br>3.3.<br>3.4.<br>3.5.                                                                         |                                         | Index register (0,0)       26         Random register (1,0)       27         EntryLo0 (2,0) and EntryLo1 (3,0) registers       28         Context (4,0)       29         PageMask Register (5,0)       29         PageGrain Register (5,1)       30         Wired register (6,0)       31                                                                                                                                                                                                                                                             | twenty one  |            |

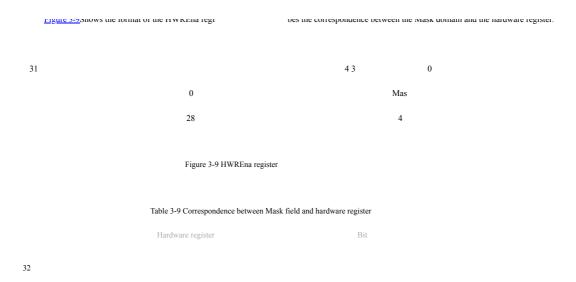

| <u>3.</u> | 3.1.<br>3.2.<br>3.3.<br>3.4.<br>3.5.<br>3.6.                                                                 |                                         | Index register (0, 0)       26         Random register (1, 0)       27         EntryLo0 (2,0) and EntryLo1 (3,0) registers       28         Context (4,0)       29         PageMask Register (5, 0)       29         PageGrain Register (5, 1)       30         Wired register (6, 0)       31         HWREna register (7, 0)       32                                                                                                                                                                                                                | twenty one  |            |

| 3.        | 3.1.<br>3.2.<br>3.3.<br>3.4.<br>3.5.<br>3.6.<br>3.7.<br>3.8.<br>3.9.                                         | CP0 cc                                  | Index register       25         Index register (0, 0)       26         Random register (1, 0)       27         EntryLo0 (2,0) and EntryLo1 (3,0) registers       28         Context (4,0)       29         PageMask Register (5,0)       29         PageGrain Register (5,1)       30         Wired register (6,0)       31         HWREna register (7,0)       32         BadVAddr register (8,0)       33                                                                                                                                           | twenty one  |            |

| 3.        | 3.1.<br>3.2.<br>3.3.<br>3.4.<br>3.5.<br>3.6.<br>3.7.<br>3.8.<br>3.9.<br>3.10                                 | . Cour                                  | Index register (0,0)       26         Random register (1,0)       27         EntryLo0 (2,0) and EntryLo1 (3,0) registers       28         Context (4,0)       29         PageMask Register (5,0)       29         PageGrain Register (5,1)       30         Wired register (6,0)       31         HWREna register (7,0)       32         BadVAddr register (8,0)       33         nt register (9,0) and Compare register (11,0)       33                                                                                                              | twenty one  |            |

| 3.        | 3.1.<br>3.2.<br>3.3.<br>3.4.<br>3.5.<br>3.6.<br>3.7.<br>3.8.<br>3.9.<br>3.10                                 | . Cour                                  | Index register       25         Index register (0, 0)       26         Random register (1, 0)       27         EntryLo0 (2,0) and EntryLo1 (3,0) registers       28         Context (4,0)       29         PageMask Register (5,0)       29         PageGrain Register (5,1)       30         Wired register (6,0)       31         HWREna register (7,0)       32         BadVAddr register (8,0)       33                                                                                                                                           | twenty one  |            |

| <u>3.</u> | 3.1.<br>3.2.<br>3.3.<br>3.4.<br>3.5.<br>3.6.<br>3.7.<br>3.8.<br>3.9.<br>3.10<br>3.11<br>3.12                 | PO ecc.                                 | Index register (0,0)       26         Random register (1,0)       27         EntryLo0 (2,0) and EntryLo1 (3,0) registers       28         Context (4,0)       29         PageMask Register (5,0)       29         PageGrain Register (5,1)       30         Wired register (6,0)       31         HWREna register (7,0)       32         BadVAddr register (8,0)       33         nt register (9,0) and Compare register (11,0)       33         vHi register (10,0)       34         us register (12,0)       35                                     | twenty one  |            |

| 3.        | 3.1.<br>3.2.<br>3.3.<br>3.4.<br>3.5.<br>3.6.<br>3.7.<br>3.8.<br>3.9.<br>3.10<br>3.11<br>3.12<br>3.13         | PO cc  CPO cc  Cour  Entry  Statu  IntC | Index register (0,0)       26         Random register (1,0)       27         EntryLo0 (2,0) and EntryLo1 (3,0) registers       28         Context (4,0)       29         PageMask Register (5,0)       29         PageGrain Register (5,1)       30         Wired register (6,0)       31         HWREna register (7,0)       32         BadVAddr register (8,0)       33         nt register (9,0) and Compare register (11,0)       33         vHi register (10,0)       34         us register (12,0)       35         tt Register (12,1)       38 | twenty one  |            |

| 3.        | 3.1.<br>3.2.<br>3.3.<br>3.4.<br>3.5.<br>3.6.<br>3.7.<br>3.8.<br>3.9.<br>3.10<br>3.11<br>3.12<br>3.13<br>3.14 | . Coun<br>Entry<br>Statu                | Index register (0,0)       26         Random register (1,0)       27         EntryLo0 (2,0) and EntryLo1 (3,0) registers       28         Context (4,0)       29         PageMask Register (5,0)       29         PageGrain Register (5,1)       30         Wired register (6,0)       31         HWREna register (7,0)       32         BadVAddr register (8,0)       33         nt register (9,0) and Compare register (11,0)       33         vHi register (10,0)       34         us register (12,0)       35                                     | twenty one  |            |

3.16. Exception Program Counter Register (14, 0) ....

3.17. Processor Revision Identifier (PRID) Register (15, 0) ... 42

I

### Page 6

#### Godson 3B1500 Processor User Manual • Volume 2

|           | 3.18. EBase Register (15, 1)                                      |

|-----------|-------------------------------------------------------------------|

|           | 3.19. Config register (16, 0) 44                                  |

|           | 3.20. Config1 register (16, 1)                                    |

|           | 3.21. Config 2 register (16, 2) 49                                |

|           | 3.22. Config 3 register (16, 3)52                                 |

|           | 3.23. Load Linked Address (LLAddr) Register (17, 0) 54            |

|           | 3.24. XContext Register (20, 0)54                                 |

|           | 3.25. Diagnostic Register (22, 0)                                 |

|           | 3.26. Debug Register (23, 0)                                      |

|           | 3.27. Debug Exception Program Counter Register (24, 0)            |

|           | 3.28. Performance Counter Register (25, 0/1/2/3) 59               |

|           | 3.29. ECC Register (26, 0) 62                                     |

|           | 3.30. CacheErr Register (27, 0/1)                                 |

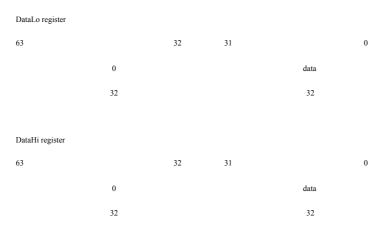

|           | 3.31. TagLo (28) and TagHi (29) Registers                         |

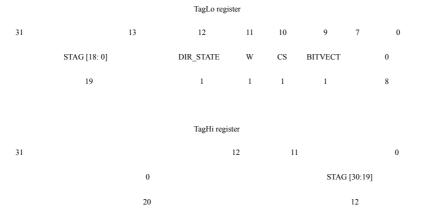

|           | 3.32. DataLo (28,1) and DataHi (29,1) registers 66                |

|           | 3.33. ErrorEPC Register (30, 0)                                   |

|           | 3.34. DESAVE register (31, 0)                                     |

|           | 3.35. CP0 instruction                                             |

| <u>4.</u> | The organization and operation of CACHE69                         |

|           | <u>4.1.</u> <u>Cache Overview</u> <u>69</u>                       |

|           | 4.1.1. Non-blocking Cache 69                                      |

|           | 4.1.2. Replacement strategy                                       |

|           | <u>4.1.3.</u> <u>Cache parameters</u>                             |

|           | 4.2. First level instruction Cache 71                             |

|           | 4.2.1. Organization of the instruction cache                      |

|           | 4.2.2. Instruction cache access                                   |

|           | 4.3. Primary Data Cache 73                                        |

|           | 4.3.1. Organization of data cache                                 |

|           | <u>4.3.2.</u> <u>Data Cache Access</u>                            |

|           | <u>4.4.</u> <u>Secondary Cache</u>                                |

|           | 4.4.1. Organization of the secondary cache                        |

|           | 4.4.2. Access to the secondary cache                              |

|           | 4.5. Cache algorithm and Cache consistency properties 76          |

|           | 4.5.1. <u>Uncached (Coherence Code 2)</u>                         |

|           | 4.5.2. Coherent cache (Cacheable coherent, consistency code 3) 77 |

|           | 4.5.3. Uncached Accelerated (consistency code 7)                  |

|           | 4.6. <u>Cache coherency</u>                                       |

|           |                                                                   |

II

Page 7

|           | <u>4.7.</u>   | Cache Commands              | 79         |            |

|-----------|---------------|-----------------------------|------------|------------|

|           | <u>4.7.1.</u> | Cache0 instruction 80       |            |            |

|           | <u>4.7.2.</u> | Cache8 instruction          |            |            |

|           | <u>4.7.3.</u> | Cache28 instruction 80      |            |            |

|           | <u>4.7.4.</u> | Cachel instruction80        |            |            |

|           | 4.7.5.        | Cache5 instruction          |            |            |

|           | <u>4.7.6.</u> | Cache9 instruction          |            |            |

|           | <u>4.7.7.</u> | Cache17 instruction 81      |            |            |

|           | <u>4.7.8.</u> | Cache21 instruction81       |            |            |

|           | <u>4.7.9.</u> | Cache25 instruction 81      |            |            |

|           | 4.7.10        | . Cache29 instruction       |            |            |

|           | 4.7.11        | Cache3 instruction          |            |            |

|           | 4.7.12        | . Cache7 instruction82      |            |            |

|           | 4.7.13        | . Cachell instruction       |            |            |

|           | 4.7.14        | . Cache19 instruction       |            |            |

|           | 4.7.15        | . Cache23 instruction82     |            |            |

|           | 4.7.16        | . Cache27 instruction82     |            |            |

|           | 4.7.17        | . Cache31 instruction       |            |            |

| <u>5.</u> | Memo          | ry management 8             | <u>5</u>   |            |

|           | <u>5.1.</u>   | Quick Lookup Table TLB      | <u> 85</u> |            |

|           | <u>5.2.</u>   | JTLB                        | <u> 85</u> |            |

|           | <u>5.2.1.</u> | Instruction TLB 86          |            |            |

|           | <u>5.2.2.</u> | Hits and failures86         |            |            |

|           | <u>5.2.3.</u> | Multiple hits               | 86         |            |

|           | <u>5.3.</u>   | Processor mode 86           |            |            |

|           | <u>5.3.1.</u> | Processor working mode      | 87         |            |

|           | <u>5.3.2.</u> | Address mode                |            |            |

|           | <u>5.3.3.</u> | Instruction Set Mode        | 87         |            |

|           | <u>5.3.4.</u> | Tail-end mode 88            | <u>}</u>   |            |

|           | <u>5.4.</u>   | Address space 88            |            |            |

|           | <u>5.4.1.</u> | Virtual address space       | 88         |            |

|           | <u>5.4.2.</u> | Physical address space      | 88         |            |

|           | <u>5.4.3.</u> | Virtual Address Translation | 88         |            |

|           | <u>5.4.4.</u> | User address space          |            | <u> 90</u> |

|           | <u>5.4.5.</u> | Manage address space 91     |            |            |

|           | <u>5.4.6.</u> | Kernel address space 92     | <u>3</u>   |            |

|           | <u>5.5.</u>   | System Control Coprocessor  | <u> 96</u> |            |

III

### Page 8

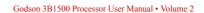

|           | 5.5.1.        | TLB entry format 96                                             |

|-----------|---------------|-----------------------------------------------------------------|

|           | 5.5.2.        | CP0 Registers 99                                                |

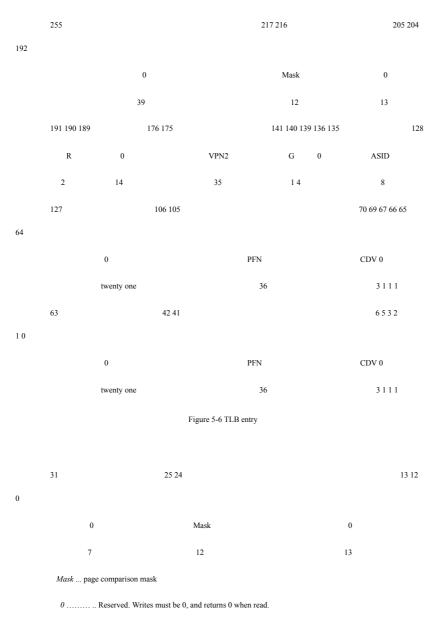

|           | <u>5.5.3.</u> | Conversion process from virtual address to physical address 100 |

|           | <u>5.5.4.</u> | TLB invalidation                                                |

|           | <u>5.5.5.</u> | TLB instruction                                                 |

|           | <u>5.5.6.</u> | Code examples                                                   |

|           | <u>5.6.</u>   | Physical address space distribution                             |

| <u>5.</u> | Proces        | sor exception105                                                |

|           | <u>6.1.</u>   | Creation and return of exceptions                               |

|           | <u>6.2.</u>   | Exception Vector Positions 105                                  |

|           | 6.3.          | Exception Priority                                              |

|           | <u>6.4.</u>   | Cold reset exception107         |       |

|-----------|---------------|---------------------------------|-------|

|           | <u>6.5.</u>   | NMI exception                   |       |

|           | <u>6.6.</u>   | Address error exception109      |       |

|           | <u>6.7.</u>   | TLB exception                   |       |

|           | <u>6.8.</u>   | TLB refill exception            |       |

|           | <u>6.9.</u>   | TLB invalid exception 111       |       |

|           | 6.10. TLE     | 3 modification exception        |       |

|           | 6.11. Cac     | he Error Exception              |       |

|           | 6.12. Bus     | Error Exception 113             |       |

|           | 6.13. Inte    | ger overflow exception          |       |

|           | 6.14. Trap    | exceptions 114                  |       |

|           | 6.15. Syst    | tem Call Exception115           |       |

|           | 6.16. Exc     | eptions to Breakpoints          | 115   |

|           | 6.17. Rese    | erved instruction exceptions    | 116   |

|           | 6.18. Cop     | processor Unavailable Exception | 11′   |

|           | 6.19. Floa    | ating point exception118        |       |

|           | 6.20. EJT     | AG exception                    |       |

|           | 6.21. Inte    | rrupt Exception118              |       |

| <u>7.</u> | Floatin       | ng-point coprocessor121         |       |

|           | <u>7.1.</u>   | <u>Overview</u>                 |       |

|           | <u>7.2.</u>   | FPU Registers 122               |       |

|           | 7.2.1.        | Floating-point registers        | . 123 |

|           | <u>7.2.2.</u> | FIR register (CP1, 0)123        |       |

|           | <u>7.2.3.</u> | FCSR register (CP1, 31)125      |       |

|           | <u>7.2.4.</u> |                                 |       |

|           | 7.2.5.        | FEXR register (CP1, 26) 127     |       |

|           |               |                                 |       |

IV

### Page 9

| <u>7.2.6.</u> | <u>FENR register (CP1, 28)</u> 128                          |

|---------------|-------------------------------------------------------------|

| <u>7.3.</u>   | Floating-point instructions 128                             |

| <u>7.3.1.</u> | List of MIPS64 compatible floating-point instructions 128   |

| <u>7.3.2.</u> | MIPS64 compatible floating-point instruction implementation |

| <u>7.3.3.</u> | Loongson custom extended floating-point instruction         |

| <u>7.4.</u>   | Floating-point part format                                  |

| <u>7.4.1.</u> | Floating-point format                                       |

| <u>7.5.</u>   | FPU instruction pipeline overview                           |

| <u>7.6.</u>   | Floating-point exception handling                           |

V

### Page 11

Godson 3B1500 Processor User Manual • Volume 2

# Map directory

| Figure 3-1 Index Register 27                          |          |

|-------------------------------------------------------|----------|

| Figure 3-2 Random Register                            |          |

| Figure 3-3 EntryLo0 and EntryLo1 registers            |          |

| Figure 3-4 Context Register                           |          |

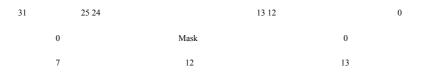

| Figure 3-5 PageMask register30                        |          |

| Figure 3-6 PageGrain Register30                       |          |

| Figure 3-7 Wired Register Limits 31                   | _        |

| Figure 3-8 Wired register                             |          |

| Figure 3-9 HWREna Register                            |          |

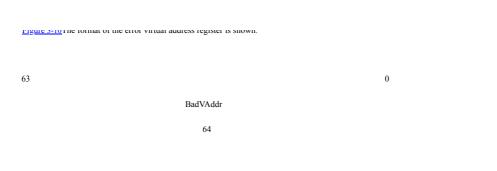

| Figure 3-10 BadVAddr register                         |          |

| Figure 3-11 Count register                            |          |

| Figure 3-12 Compare register34                        |          |

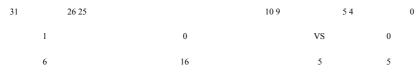

| Figure 3-13 EntryHi register                          |          |

| Figure 3-14 Status register                           |          |

| Figure 3-15 IntCtl register                           |          |

| Figure 3-16 SRSCtl register                           |          |

| Figure 3-17 Cause Register                            | <u>)</u> |

| Figure 3-18 EPC register 42                           |          |

| Figure 3-19 Processor Revision Identifier Register 43 |          |

| Figure 3-20 Ebase Register 44                         |          |

| Figure 3-21 Config register                           |          |

| Figure 3-22 Config1 register                          |          |

| Figure 3-23 Config2 register 50                       |          |

| Figure 3-24 Config3 register53                        |          |

| Figure 3-25 LLAddr Register                           |          |

| <u>Figure 3-26 XContext register</u> 55               |          |

| <u>Figure 3-27 Diagnostic Register</u> 56             |          |

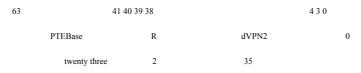

| Figure 3-28 Debug register 57                         |          |

Figure 3-29 DEPC register 59

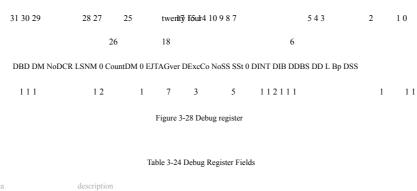

Figure 3-30 Performance counter register 60

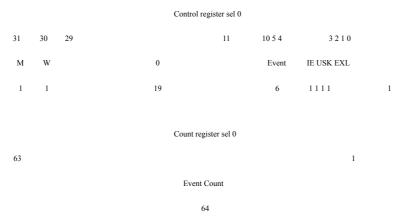

Figure 3-31 ECC register 63

VII

### Page 12

#### Godson 3B1500 Processor User Manual • Volume 2

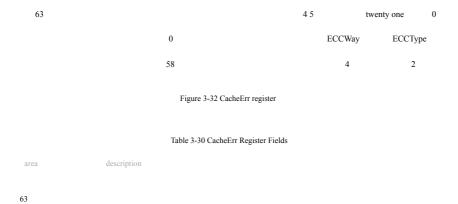

| Figure 3-32 CacheErr register 63                                                    |

|-------------------------------------------------------------------------------------|

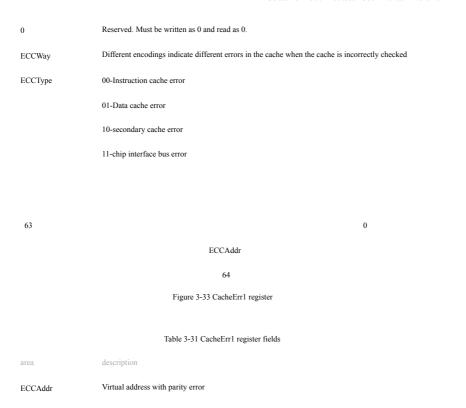

| Figure 3-33 CacheErr1 register                                                      |

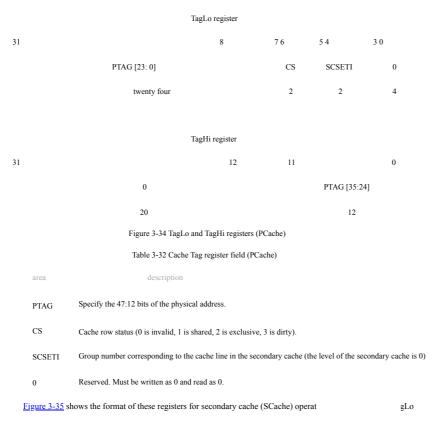

| Figure 3-34 TagLo and TagHi registers (PCache) 65                                   |

| Figure 3-35 TagLo and TagHi registers (SCache) 65                                   |

| Figure 3-36 DataLo and DataHi registers                                             |

| Figure 3-37 ErrorEPC register                                                       |

| Figure 3-38 DESAVE register 67                                                      |

| Figure 4-1 Organization of Instruction Cache                                        |

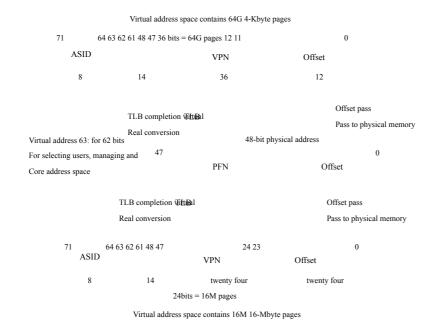

| Figure 5-1 Overview of Virtual-to-Real Address Translation                          |

| Figure 5-2 64-bit mode virtual address translation 90                               |

| Figure 5-3 Overview of user virtual address space in user mode                      |

| Figure 5-4 User space and management space in management mode92                     |

| Figure 5-5 Overview of user, management, and kernel address space in kernel mode 95 |

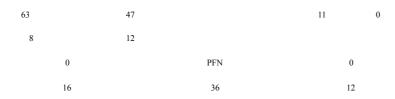

| Figure 5-6 TLB entry 97                                                             |

| Figure 5-7 PageMask register 97                                                     |

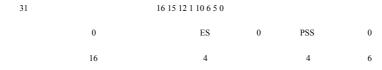

| Figure 5-8 EntryHi register 98                                                      |

| Figure 5-9 EntryLo0 and EntryLo1 registers                                          |

| Figure 5-10 TLB address translation101                                              |

| Figure 7-1 Organizational Structure of Functional Units in Godson 3A Architecture   |

| Figure 7-2 Floating point register format                                           |

| Figure 7-3 FIR register 124                                                         |

| Figure 7-4 FCSR register                                                            |

| Figure 7-5 FCCR register                                                            |

| <u>Figure 7-6 FEXR register</u>                                                     |

| Figure 7-7 FENR register 128                                                        |

| Figure 7-8 Floating-point format                                                    |

VIII

### Godson 3B1500 Processor User Manual • Volume 2

### Table of contents

| Table 2-1 CPU instruction set: fetch instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>Table 2-2 CPU instruction set: Arithmetic instruction (ALU immediate value)</u> 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <u>Table 2-3 CPU instruction set: Arithmetic instructions (3 operands)</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <u>Table 2-4 CPU instruction set: Arithmetic instructions (2 operands)</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <u>Table 2-5 CPU instruction set: multiplication and division instructions</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Table 2-6 CPU instruction set: shift instruction9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Table 2-7 CPU instruction set: branch and branch instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Table 2-8 CPU instruction set: CP0 instruction11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Table 2-9 CPU instruction set: special instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Table 2-10 CPU instruction set: exception instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Table 2-11 CPU instruction set: conditional move instruction 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Table 2-12 CPU instruction set: other instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Table 2-13 Instruction with implementation differences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Table 2-14 Disable instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Table 2-15 Custom extended fetch instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Table 2-16 User-defined extended multiplication and division instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Table 2-17 Custom Extension X86 Binary Translation Acceleration Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <u>Table 2-17 Custom Extension X86 Binary Translation Acceleration Instructions</u> 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Table 2-17 Custom Extension X86 Binary Translation Acceleration Instructions       19         Table 2-18 Custom extended 64-bit multimedia acceleration instructions       twenty one                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Table 2-17 Custom Extension X86 Binary Translation Acceleration Instructions       19         Table 2-18 Custom extended 64-bit multimedia acceleration instructions       twenty one         Table 2-19 Custom extended miscellaneous instructions       twenty one                                                                                                                                                                                                                                                                                                                                                                                                   |

| Table 2-17 Custom Extension X86 Binary Translation Acceleration Instructions       19         Table 2-18 Custom extended 64-bit multimedia acceleration instructions       twenty one         Table 2-19 Custom extended miscellaneous instructions       twenty one         Table 3-1 CP0 register       25                                                                                                                                                                                                                                                                                                                                                           |

| Table 2-17 Custom Extension X86 Binary Translation Acceleration Instructions     19       Table 2-18 Custom extended 64-bit multimedia acceleration instructions     twenty one       Table 2-19 Custom extended miscellaneous instructions     twenty one       Table 3-1 CP0 register     25       Table 3-2 Description of each field of the Index register     27                                                                                                                                                                                                                                                                                                  |

| Table 2-17 Custom Extension X86 Binary Translation Acceleration Instructions       19         Table 2-18 Custom extended 64-bit multimedia acceleration instructions       twenty one         Table 2-19 Custom extended miscellaneous instructions       twenty one         Table 3-1 CP0 register       25         Table 3-2 Description of each field of the Index register       27         Table 3-3 Fields of Random Register       27                                                                                                                                                                                                                           |

| Table 2-17 Custom Extension X86 Binary Translation Acceleration Instructions 19 Table 2-18 Custom extended 64-bit multimedia acceleration instructions twenty one Table 2-19 Custom extended miscellaneous instructions twenty one Table 3-1 CP0 register 25 Table 3-2 Description of each field of the Index register 27 Table 3-3 Fields of Random Register 27 Table 3-4 EntryLo register field 28                                                                                                                                                                                                                                                                   |

| Table 2-17 Custom Extension X86 Binary Translation Acceleration Instructions19Table 2-18 Custom extended 64-bit multimedia acceleration instructionstwenty oneTable 2-19 Custom extended miscellaneous instructionstwenty oneTable 3-1 CP0 register25Table 3-2 Description of each field of the Index register27Table 3-3 Fields of Random Register27Table 3-4 EntryLo register field28Table 3-5 Context register fields29                                                                                                                                                                                                                                             |

| Table 2-17 Custom Extension X86 Binary Translation Acceleration Instructions19Table 2-18 Custom extended 64-bit multimedia acceleration instructionstwenty oneTable 2-19 Custom extended miscellaneous instructionstwenty oneTable 3-1 CP0 register25Table 3-2 Description of each field of the Index register27Table 3-3 Fields of Random Register27Table 3-4 EntryLo register field28Table 3-5 Context register fields29Table 3-6 Mask values for different page sizes30                                                                                                                                                                                             |

| Table 2-17 Custom Extension X86 Binary Translation Acceleration Instructions 19  Table 2-18 Custom extended 64-bit multimedia acceleration instructions twenty one  Table 2-19 Custom extended miscellaneous instructions 25  Table 3-1 CP0 register 25  Table 3-2 Description of each field of the Index register 27  Table 3-3 Fields of Random Register 27  Table 3-4 EntryLo register field 28  Table 3-5 Context register field 29  Table 3-6 Mask values for different page sizes 30  Table 3-7 PageGrain Register Field 31                                                                                                                                      |

| Table 2-17 Custom Extension X86 Binary Translation Acceleration Instructions 19 Table 2-18 Custom extended 64-bit multimedia acceleration instructions twenty one Table 2-19 Custom extended miscellaneous instructions 25 Table 3-1 CP0 register 25 Table 3-2 Description of each field of the Index register 27 Table 3-3 Fields of Random Register 27 Table 3-4 EntryLo register field 28 Table 3-5 Context register fields 29 Table 3-6 Mask values for different page sizes 30 Table 3-7 PageGrain Register Field 31 Table 3-8 Wired register fields 32                                                                                                           |

| Table 2-17 Custom Extension X86 Binary Translation Acceleration Instructions 19 Table 2-18 Custom extended 64-bit multimedia acceleration instructions twenty one Table 2-19 Custom extended miscellaneous instructions 25 Table 3-1 CP0 register 25 Table 3-2 Description of each field of the Index register 27 Table 3-3 Fields of Random Register 27 Table 3-4 EntryLo register field 28 Table 3-5 Context register field 29 Table 3-6 Mask values for different page sizes 30 Table 3-7 PageGrain Register Field 31 Table 3-8 Wired register fields 32 Table 3-9 Correspondence between Mask field and hardware register 32                                       |

| Table 2-17 Custom Extension X86 Binary Translation Acceleration Instructions 19 Table 2-18 Custom extended 64-bit multimedia acceleration instructions twenty one Table 2-19 Custom extended miscellaneous instructions 25 Table 3-1 CP0 register 25 Table 3-2 Description of each field of the Index register 27 Table 3-3 Fields of Random Register 27 Table 3-4 EntryLo register field 28 Table 3-5 Context register fields 29 Table 3-6 Mask values for different page sizes 30 Table 3-7 PageGrain Register Field 31 Table 3-8 Wired register fields 32 Table 3-9 Correspondence between Mask field and hardware register 32 Table 3-10 EntryHi register field 34 |

IX

### Page 14

| Table 3-13 SRSCtl Register Fields              |

|------------------------------------------------|

| Table 3-14 Cause register fields 40            |

| Table 3-15 ExcCode field of the Cause register |

| Table 3-16 PRId register fields                |

| Table 3-17 Ebase register fields               |

| Table 3-18 Config register field               |

| Table 3-19 Config1 register field              |

| Table 3-20 Config2 register field              |

| Table 3-21 Config3 register field                    |               |          |

|------------------------------------------------------|---------------|----------|

| Table 3-22 XContext register fields                  |               |          |

| <u>Table 3-23 Diagnostic register fields</u>         |               |          |

| Table 3-24 Debug register fields                     |               |          |

| Table 3-25 Performance counter list                  |               | 59       |

| Table 3-26 Count enable bit definition               | <u>60</u>     |          |

| Table 3-27 Counter 0 events                          |               |          |

| Table 3-28 Counter 1 events                          |               |          |

| Table 3-29 Fields of ECC Register                    |               |          |

| Table 3-30 CacheErr Register Fields                  |               |          |

| Table 3-31 CacheErr1 register fields 64              |               |          |

| Table 3-32 Cache Tag Register Field (PCache)         | <u>65</u>     |          |

| Table 3-33 Cache Tag Register Field (SCache)         | <u>66</u>     |          |

| Table 3-34 CP0 instruction                           | 67            |          |

| Table 4-1 Cache parameters                           | <u>70</u>     |          |

| Table 4-2 Consistency Attributes of Godson 3 Cache   | <u>76</u>     |          |

| Table 4-3 GS464 Cache Consistency Properties         | <u>79</u>     |          |

| Table 5-1 Working mode of the processor              | 8′            | <u>7</u> |

| Table 5-2 Value of C bit on TLB page                 | 99            |          |

| Table 5-3 CP0 registers related to memory management | 99            |          |

| Table 5-4 TLB instruction                            | 102           |          |

| Table 6-1 Exception vector base address              | : 10 <u>5</u> |          |

| Table 6-2 Exception Vector Offset                    | 106           |          |

| Table 6-3 Exception priority                         |               |          |

| Table 7-1 FIR register fields                        |               |          |

| Table 7-2 FCSR register fields                       |               |          |

| X                                                    |               |          |

### Page 15

| Table 7-3 Round Mode Decoding                                                                              |

|------------------------------------------------------------------------------------------------------------|

| Table 7-4 FIPS Instruction Set of MIPS64                                                                   |

| <u>Table 7-5 Custom extended floating-point fetch instructions</u>                                         |

| <u>Table 7-6 Custom extended floating point format conversion instructions</u>                             |

| Table 7-7 Formulas for calculating the values of floating point numbers in single and double precision 133 |

| Table 7-8 Floating point format parameter values                                                           |

| <u>Table 7-9 Floating point values for the maximum and minimum numbers</u>                                 |

| Table 7-10 Default handling of exceptions 136                                                              |

ΧI

#### Page 16

Godson 3B1500 Processor User Manual • Volume 2

#### Structure overview

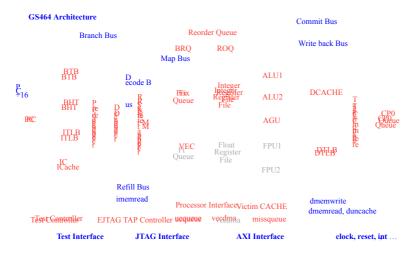

GS464 is a general-purpose RISC processor IP that implements the 64-bit MIPS64 instruction set. GS464 instruction pipeline Each clock cycle takes four instructions to decode, and dynamically sends them to five full-flow functional units. Although the instructions are in Out-of-order execution is performed under the premise of ensuring dependencies, but the instructions are submitted in the original order of the program to ensure accurate examples Out and fetch sequentially.

The four-shot superscalar structure makes the instruction and data related issues in the instruction pipeline very prominent. GS464 uses out of order Execution technology and aggressive storage system design to improve pipeline efficiency.

Out-of-order execution techniques include register renaming techniques, dynamic scheduling techniques, and branch prediction techniques. Register renaming solution WAR (read-after-write) is related to WAW (write-after-write) and is used for accurate on-site recovery caused by exceptions and false branch prediction, GS464 performs fixed-point renaming through a 64-item physical register file. Dynamic scheduling based on the number of times the instruction operands are ready Order instead of the order in which the instructions appear in the program to execute instructions, reducing blocking caused by RAW (read after write), GS464 There is a 16-term fixed-point reservation station and a 16-term floating-point reservation station for out-of-order transmission, and a 64-term The Reorder queue (referred to as ROQ) implements instructions that are executed out of order and submitted in the order of the program. Branch prediction Whether the shift instruction successfully jumped to reduce the control-related blocking. The GS464 uses 16-bit branch target address buffers. Branch Target Buffer (BTB), Branch History Table for 2K entries,

(BHT for short), 9-bit Global Histiry Registor (GHR for short), and return of 4 items

The address stack (Return Address Stack, RAS for short) performs branch prediction. GS464 has two 64-bit full pipeline

Point feature

GS464 advanced storage system design can effectively improve the efficiency of the pipeline. GS464 Level 1 Cache consists of 64KB

Instruction cache (four-way group associative) and 32KB data cache (two-way group associative). GS464 TLB has 64

The items adopt a fully associative structure, and each item can map an odd page and an even page. The page size is variable from 4KB to 16MB.

GS464 dynamically resolves address dependencies through a 16-item fetch queue and an 8-item fetch queue.

Lai, to achieve out-of-order execution of memory access operations, non-blocking cache, load instruction speculation execution (Load Speculation), etc.

#### Godson 3B User Manual 2

Fetch optimization technology. GS464 supports 128-bit fetch operation, and its virtual address and physical address are 48 bits.

GS464 supports MIPS company's EJTAG debugging specification, adopts standard AXI interface, and its instruction cache implements

Parity check, data cache implements ECC check. The above characteristics can increase the applicable scope of Godson-3.

The basic pipeline of GS464 includes instruction fetch, pre-decoding, decoding, register renaming, scheduling, transmitting, reading registers,

Execution, submission and other 9 levels, each level of the pipeline includes the following operations.

1

#### Page 17

#### Godson 3B1500 Processor User Manual • Volume 2

- ◆ The instruction pipeline uses the value of the program counter PC to access the instruction cache and instruction TLB. If the instruction cache

And instruction TLB are hit, then four new instructions are fetched into the instruction register IR.

- ◆ The pre-decoding pipeline stage decodes the branch instruction and predicts the direction of the jump.

- ♦ The decoding pipeline converts the four instructions in IR into the internal instruction format of GS464 and sends them to the register renaming module.

Piece.

♦ Register renaming pipeline allocates a new physical register for the logical target register and registers the logical source

The device is mapped to the physical register that was most recently assigned to it.

- ◆ Scheduling pipeline assigns renamed instructions to fixed-point or floating-point reservation stations for execution, and sends them to ROQ at the same time

For sequential submission after execution; in addition, branch instructions and fetch instructions are also sent to the transfer queue and fetch

Store queue.

- ◆ The launch pipeline selects one of each function from the fixed-point or floating-point reservation station. All operands are ready.

Instructions; instructions not ready for operands when renaming, by listening to the result bus and forward bus, etc.

Wait for its operands to be ready.

- ◆ The read register pipeline is the instruction issued by the upper-level water stage to read the corresponding source operand from the physical register file

To the corresponding functional components.

- ◆ The execution pipeline executes the instruction according to the instruction type and writes the calculation result back to the register file; the result bus is also sent to

The station and register renaming tables are reserved to inform the corresponding register values that they are ready for use.

- ♦ The submission pipeline submits the executed instructions in the order of the programs recorded in the Reorder queue.

Four more instructions can be submitted per shot, and the submitted instructions are sent to the register rename table for confirmation of its purpose.

Device renames the relationship and releases the physical register originally allocated to the same logical register, and sends it to the fetch queue

Allow those committed instructions to be written to the cache or memory.

The above is the pipeline of basic instructions. For some more complex instructions, such as fixed-point multiply-divide instructions, floating-point instructions,

Fetching instructions requires multiple shots during execution. The basic structure of GS464 is shown in the figure below.

2

#### Page 18

#### Godson 3B1500 Processor User Manual • Volume 2

Figure 1-1 Basic structure of GS464 processor

3

Page 20

Godson 3B1500 Processor User Manual • Volume 2

### 2. Overview of Godson GS464 processor core instruction set

The Loongson GS464 processor core is compatible with the MIPS64 R2 architecture, which implements all the definitions of the MIPS64 R2 specification.

Set of required instructions, as well as some custom extension instructions.

Godson GS464 core processor implemented in the MIPS64 R2 compatible instructions include 2 section 5.1 in. For reasons of space,

The detailed definitions of these instructions are not given in this document. Readers do need to know the detailed definition of the relevant directives

MIPS Architecture Specification Volume I and Volume II version 2.50. The implementation-related content in this part of the instructions will be in section 2.2

As explained in the article, the implementation of several other MIPS64 R2 instructions GS464 processor core is not the same as the MIPS architecture specification.

This is also explained in section 2.2.

Godson custom extension instructions implemented by the processor core GS464 recited in 2. Section 1.3. For reasons of length, this one

The detailed definition of the sub-instruction is not given in this document. Readers do need to know the detailed definitions of the relevant directives.

Instruction System Manual. The Loongson Instruction System Manual is currently only available to authorized customers.

#### 2.1. MIPS64 Compatible Instruction List

According to the instruction function, the MIPS64 compatible instructions implemented by the GS464 processor core can be divided into the following groups:

- ◆ Fetch instruction

- ◆ Operation instructions

- Branch and jump instructions

- ◆ Coprocessor instructions

- ◆ Other instructions

### 2.1.1. Fetch instruction

$The \ MIPS \ architecture \ uses \ a \ load \ / \ store \ architecture. \ All \ operations \ are \ performed \ on \ registers, \ and \ only \ fetch \ instructions \ can$

Access to stored data. Fetch instructions include reading and writing of various widths of data, unsigned reads, non-aligned fetches and atomic fetch

Save, etc.

Table 2-1 CPU instruction set: fetch instruction

| Instruction mnemonics | Brief instruction function | ISA compatibility level |

|-----------------------|----------------------------|-------------------------|

| LB                    | Fetch bytes                | MIPS32                  |

Page 21

| Instruction mnemonics | Brief instruction function             | ISA compatibility level |